細田 隆之

Oct. 10, 2007

English edition is here.

English edition is here.| 上面図 | バッテリカバーを外した 底面図 |

4箇所の溶着部と 薄板用ドリル (3.8mm) |

溶着部の上部 1.5mm を 削り取る |

|

|

|

|

| 上端が開いたところ | 見えない4箇所の溶着部を 外してケースが分離した |

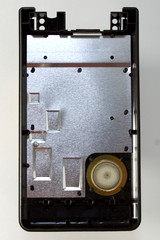

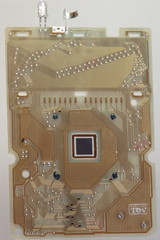

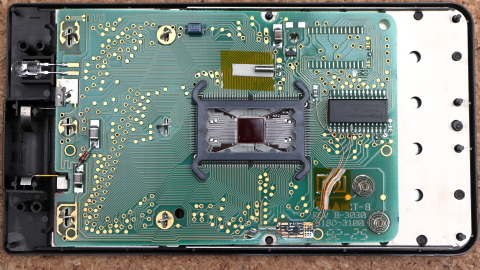

バックプレートと圧電ブザー | プリント基板上に MPU と SRAM が1個乗っている |

|

|

|

|

| SRAM と ROM パッド部の 拡大図 |

8KB SRAM を取り外した (洗浄前なのでちょっと汚い) |

ジャンパ設定を変更して 32KB SRAM を実装 フラックスを取り除きさらに洗浄した |

|

|

|

|

元々付いていた S-MOS system の 8KB SRAM SOIC パッケージ 省電力品の 32KB SRAM と交換した。 ここで使ったのは Cypress の |

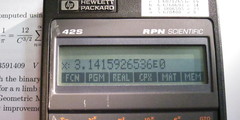

| Available Memory: 31533 Bytes (ファームウェア Rev.C) |

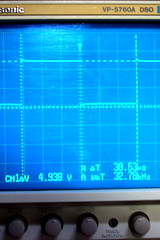

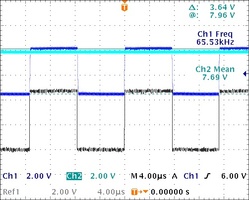

おまけ 1 *note1 クロックバッファ出力波形 fclock = 32.768kHz |

おまけ 2 *note2 SRAM の Vdd 端雑音波形 SRAM の _WR 波形 |

おまけ 3 *note3, *note13 固体タンタルコンデンサを 積層セラミックに交換 |

|

|

|

|

クロック発振器のバッファ出力らしきテストポイントが水晶発振子の隣にあって、 この写真はそこの波形と*note2 : 雑音と波形

32.78kHz (実際には周波数カウンタで測定すると 32.768kHz) の周波数を表している。

これらの波形は下記のテストプラグラムを実行中に測定した。*note3 : コンデンサの交換 (随意)

SRAM の Vdd 端子での雑音は許容できる程度で RAM_WR の波形もそんなに悪くなかった。

00 { 15-Byte Prgm } 01 LBL "W" 02 STO "C" 03 CLX 04 RCL "C" 05 GTO "W" 06 .END.

これらの固体タンタルコンデンサを積層セラミックコンデンサに交換することにより*note4 : 電源電流 (fclock=32.768kHz, Vbattery=4.70V(SR44×3), Ta=26°C)

その洩れ電流を低減し、また寿命と信頼性を改善することが出来る。

大きい方の 100μF/6.3V のコンデンサは電源のデカップリング用で、

他の小さいのは LCD 用の昇圧回路の平滑用である。

ここで使用したコンデンサは、TDK の最新の高性能コンデンサ(部品の型番は下に記す) なので、まだ幾分高価である。

元の部品パッドは C3225 サイズのコンデンサには、ぎりぎりにしか適合しないので 注意が必要である。

TDK C3225(EIA CC1210) 100μF±20%/6.3V C3225JB0J107M

TDK C3225(EIA CC1210) 10μF±20%/16V C3225JB1C106M

そういう意図ではないが、 SRAM の Vdd 端子での雑音は このコンデンサ交換ではそんなには低減されなかった。

SRAM とプロセッサの間のパッドに 100nF〜1uF の積層セラミックコンデンサを実装して、 それの電源のデカップリングにするのもよい。

Irun≈3.3mA*note5 : SR44 の標準容量は 165mAh。

Iidle≈380μA

Istandby≈8.9μA

スタンバイ電流測定用抵抗 (1kΩ±0.05%//10μF±20%)

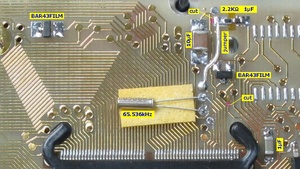

| 元の 32.768kHz の 水晶振動子を外す |

65.536kHz の水晶振動子を 実装する |

元の波形 クロック (上) と SRAM_WR (下) |

修正後の波形 クロック (上) と SRAM_WR (下) |

|

|

|

|

Ta=27°C Oscillator frequency [kHz] Comment Vbattery 65.536 100.000 131.072 4.7V O.K. O.K. O.K. Nominal voltage of SR44×3 at 20°C 3.8V Cut-off voltage of SR44×3 at -10°C 3.7V ROM O.K.

DRAM FAIL

URAM O.K.ROM O.K.

DRAM FAIL

URAM O.K.- 3.4V 3.0V cann't turn on cann't turn on Low battery indicator turns on when

Vbattery ≤ 3.0V2.9V 2.8V ROM O.K.

DRAM FAIL

URAM O.K.2.7V Cut-off voltage of LR44×3 at 20°C

Irun ≈ 5.3mA*note7 : 電源電流 (fclock=65.536kHz, *(0x40300)==0xF, Vbattery=4.71V(SR44×3), Ta=23°C)

Iidle ≈ 440μA(typ.) (420μA/minimum contrast ~ 560μA/maximum contrast)

Iidle ≈ 440μA(typ.) (420μA/minimum contrast ~ 520μA/maximum contrast, Diode=BAR43CFILM)

Istandby ≈ 15 μA

Istandby ≈ 14.9 μA (Diode=BAR43CFILM)

Isleep ≤ 100 nA *note15

Irun ≈ 7.6mA

Iidle ≈ 480μA(typ.)

y:8*note9 : 重量

x:876

6:07.5 [min:sec] HP-42S (Rev.C) Keystroke / RPN / fosc=65.536kHz

3:28.0 [min:sec] HP-42S (Rev.C) Keystroke / RPN / fosc=65.536kHz / fast mode

136.0g + 6.6g(batteries)

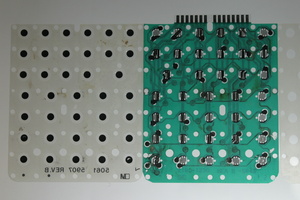

| PCB の裏面 (ファームウェア Rev.A) |

LCD の裏面 |

LCD アセンブリ内側の埃を HFC134a のエアロダスター ZC-32 で吹き飛ばして除去 |

PCB の改造後の上面 |

バックプレート Kapton®テープ付加*note13 |

|

|

|

|

|

Irun ≈ 5.0mA*note11 : 電源電流 (fclock=65.536kHz, *(0x40300)==0xf, Vbattery=4.50V(SR44×3), Ta=22°C)

Iidle ≈ 440μA(typ.) (400μA/minimum contrast ~ 540μA/maximum contrast)

Iidle ≈ 380μA(typ.) (340μA/minimum contrast ~ 420μA/maximum contrast, Diode=BAR43CFILM)

Istandby ≈ 14 μA

Istandby ≈ 13.5 μA (Diode=BAR43CFILM)

Isleep ≤ 100 nA

Irun ≈ 6.8mA*note12 : Calculator Benchmark (N-queen problem) の結果

Iidle ≈ 440μA(typ.)

y:8*note13 : バックプレートに Kapton® テープ付加

x:876

5:48.2 [min:sec] HP-42s (REv.A) Keystroke / RPN / fosc=65.536kHz

3:30.4 [min:sec] HP-42s (Rev.A) Keystroke / RPN / fosc=65.536kHz / fast mode

100μF の固体タンタルコンデンサを積層セラミックコンデンサに交換した場合は、コンデンサ上部の*note14 : 重量

バックプレートに Kapton®テープなどの強靭な絶縁テープを付加し不慮の短絡事故を防ぐべきである。

139.5g + 6.6g(電池)*note15 : ディープスリープモード

[EXIT] と [+] と [XEQ] を同時に押すとディープスリープモードに入ります。

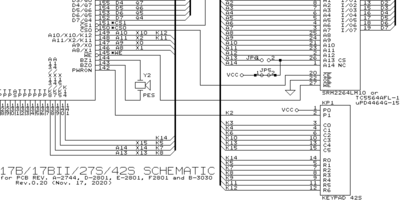

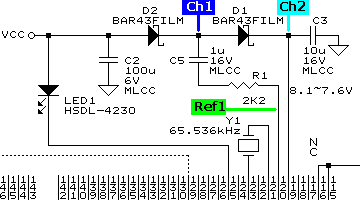

回路図 (316KB png)

Rev.0.20 : Nov. 17 2020 : L1R2 のピンアサインを修正しました。

Rev.0.16 : Jan. 30, 2010

Rev.0.15 : Jan. 27, 2010

Rev.0.14 : Dec. 22, 2009

| 壊れているメンブレン・スイッチ | 移植後のメンブレン・スイッチ | 部品の移植元と提供先 |

|

|

|

| 改造した LCD バイアス電圧発生器 | プリント基板の改造箇所 | 電圧波形 |

|

|

|

Iidle ≈ 450μA(typ.) (440μA/minimum contrast ~ 550μA/maximum contrast)

Istandby ≈ 22 μA

Isleep ≈ 660 nA

HP 42S のバス制御線の波形

ch1:*CS, ch2:AS (2V/div, 1μ/s, Vdd=4.2V, Ta=25°C)

配線とデカップリングコンデンサhp42s/NV-RAM 回路図

FRAM(FM18W08-SG)のクロースアップ

多機能ゲート(SN74LVC1G97)のクロースアップ

SN=3005S02826

クリックで全回路図 (155KB gif)

Rev.0.19 : Dec. 11, 2013

HP 42S/NV は供給電圧が 2.9V に下がるまで動作し続けました。*note17 : 電源電流 (fclock=65.536kHz, Vbattery=4.70V(SR44×3), Ta=25°C, SN=3005S02826/FM28W08-SGTR)

次の状況を乗り越えて計算機の内容は生き残りました。

- バッテリの取り外し

- バッテリ端子間の短絡

- スタンバイ(電源オフ)状態で供給電圧が徐々に 0Vまで低下

- アイドル(電源オン)状態で供給電圧が徐々に 0Vまで低下

- プログラム実行中に供給電圧が徐々に 0Vまで低下

Irun ≈ 3.97mA*note18 : 電源電流 (fclock=65.536kHz, Vbattery=4.70V(SR44×3), Ta=25°C, SN=3242S09191/FM28W08-SGTR)

Iidle ≈ 445μA

Istandby ≈ 31.7μA

Isleep ≈ 17.5μA

Irun ≈ 4.13mA

Iidle ≈ 476μA

Istandby ≈ 22.84μA

Isleep ≈ 7.52μA

"HP 42S のメモリーを 32KB にアップグレード" のときの 42S に "32Kバイト不揮発性メモリで倍速の HP 42S" と同じ改造を施し、 併せて固体タンタルキャパシタを2個の MLCC と1本の保護用ショットキーダイオードに交換しました。 このダイオードは ESD や電池の逆挿入からプロセッサやメモリーを保護してくれるかも知れません。

hp42s/NV-RAM / MLCC and SiSBD schematic diagramクリックで全回路図 (400KB png)交換した部品

Rev.0.20 : Nov. 17, 2020 : L1R2 のピンアサインを修正しました。

DUT = BAT43, Ir ≈ 40 nA (Ta = 21 °C, Vr = 5 V), Vf ≈ 304mV (Ta = 21 °C, If = 2 mA)

電源のオン・オフサイクルのリセット時に マイクロプロセッサのピンが高インピーダンス状態になる ことが想定されるため、その間 FRAM の *CE ピンを 'High' に保持するためにプルアップが必要です。hp42s/NV-RAM/LDO 回路図

FRAM, LDOレギュレータ, デカップリングコンデンサとプルアップ抵抗

SN=2909S32377

クリックで全回路図 (43KB gif)*note19 : 電源電流 (fclock=65.536kHz, Vbattery=4.70V(SR44×3), Vcc=3.30V, Ta=25°C)

Rev.0.19x : Dec. 15, 2013

Isleep ≈ 133μAお断り

これらの改造は実験的なもので結果を保障されたものと考えてはなりません。 ここに記載してある内容は筆者による改造の推奨もそそのかしも意図していません。

MoHPC HP Articles Forum, Increasing HP-42s Memory to 32K, Paul J. Brogger他には

MoHPC HP Articles Forum, Pioneer keyboard schematic, Randy Slayer

HP pioneer series calculator internals追補 - プログラムライブラリ

Hewlett-Packard Calculator - Eric's site

www.finseth.com - HPDATAbase

www.hp42s.com - Home on the net for everything HP-42S

www.hpmuseum.org - The Museum of HP Calculators

MoHPC HP Articles Forum, Pioneer "Observational Internals", Paul J. Brogger

MoHPC HP Articles Forum, HP-42S: New Facts, J-F Garnier

HP-42S Fast Mode under program control, Gene

Cypress

TDK

Maxell

![[Mail]](/~lyuka/images/mail.gif)

© 2000 Takayuki HOSODA.

© 2000 Takayuki HOSODA.