(19) **日本国特許庁(JP)**

# (12) 特許公報(B1)

(11)特許番号

特許第6172726号 (P6172726)

(45) 発行日 平成29年8月2日(2017.8.2)

(24) 登録日 平成29年7月14日 (2017.7.14)

(51) Int. Cl. FL

HO3B 28/00 (2006, 01) нозв 28/00 Α

請求項の数3 (全 10 頁)

(21) 出願番号

特願2016-76487 (P2016-76487)

(22) 出願日 審查請求日 平成28年4月6日(2016.4.6) 平成28年4月6日(2016.4.6) ||(73)特許権者 503378475

有限会社ファインチューン

神奈川県横浜市鶴見区鶴見中央三丁目10

番26号

(74)代理人 100106002

弁理士 正林 真之

(74)代理人 100120891

弁理士 林 一好

(72) 発明者 細田 隆之

横浜市鶴見区鶴見中央三丁目10番26号

有限会社ファインチューン内

審査官 石田 昌敏

最終頁に続く

## (54) 【発明の名称】数値制御波形発生器及びデジタル同期検波器

## (57)【特許請求の範囲】

### 【請求項1】

基本波を表す各数値を含む数表を用いて所定の波形を発生させる数値制御波形発生器に おいて、

前記基本波の波形の1周期、

当該基本波に振幅軸と時間軸とのうち少なくとも一方に対して対称性がある場合には当該 基本の1/2周期、

#### 又は

当該基本波に振幅軸及び時間軸の夫々に対して対称性がある場合には1/4周期を、

10 予め設定されたP個(Pは、1以上の整数値)の素数で、均等分割したときにおける、各 時刻での各振幅値を、前記各数値として含む数表と、

所定の読み出し方を変える制御を実行することで、当該基本波の整数倍周波数の波形を 1以上発生させる読み出し制御部と、

を備える数値制御波形発生器。

#### 【請求項2】

前記数表は、

前記基本波の波形の元となる波形が、直流分を含まない波形の場合には、当該波形を示 す関数の零交差点がサンプリング点とならないように位相を調整して得た整数を、前記各 数値として含む、

請求項1に記載の数値制御波形発生器。

### 【請求項3】

請求項1または2に記載の数値制御波形発生器を数値局部発振器として用いるデジタル 同期検波器。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、数値制御波形発生器(以下、「NCWG」と呼ぶ)に関し、特に、送受信信号を離散的数値のデジタル信号で扱う同期検波器(以下、「デジタル同期検波器」と呼ぶ)の、数値的局部発振器(以下、「NLO」と呼ぶ)として用いるNCWG及びデジタル同期検波器に関する。

10

【背景技術】

[0002]

デジタル同期検波機では、数値的周波数変換器(以下、「数値ミキサー」と呼ぶ)のNLOに用いられるNCWGの信号のスプリアスが、イメージ妨害や微小な信号を検波する場合に信号検知レベルの下限を決める重要な要素となっている。

従来より、NCWGとしては、数値的な帰還による数値的な発振回路によって正弦波や、それに直交する余弦波を同時に生成したりするもの(以下、「NCO」と呼ぶ)(例えば特許文献 1 参照)や、基本波の波形を数表(ルックアップテーブル)として作成しておき、生成する周波数に応じて読み出し方を変えるものがある(例えば特許文献 2 参照)。

[0003]

20

特許文献1に記載のNCOでは、誤差の蓄積や安定度の点から、出力として必要とする以上の数値分解能が必要である。このため、NCOでは、発生させる周波数によりスプリアスの発生具合が変動する。よって、NCOは、簡易なデジタル通信などには適しているものの、微小な受信信号の変化を検知するような目的(以下、「微弱信号検知」と呼ぶ)には余り適していない。

一方、特許文献 2 に記載の N C W G では、出力として必要とするビット数が決まれば、全ての発生させうる信号について数表により一意に定まるため、スプリアスの予測が可能で微弱信号検知に適している。

【先行技術文献】

【特許文献】

30

[0004]

【特許文献1】特開平9-135364号公報

【特許文献2】特開2000-252750号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

しかしながら、NCWGにより単一、又は複数の周波数の信号を発生させる場合、単一の正弦波、又は複数の正弦波を適当な位相と振幅で加算した波形を生成しようとしても、量子化誤差のために目的の周波数以外の信号、即ちスプリアスが発生すること自体を避けることはできない。

40

この量子化誤差に起因するスプリアスを低減するには、一義的には量子化ビット数を増やし、又は併せてサンプリングレートを増大させる必要があるが、どちらも物理的な制約を受ける。

[0006]

ここで、NCWGにより発生させる波形が、上記の正弦波のように一周期の間に絶対値が同じ振幅値を周期的に通る波形において、基本波の数表を用いてその整数倍周波数の波形を生成する場合に、生成する波形の基本波に対する倍数と数表の波形分割数が小さな整数比(以下単に、「小さな整数比」と略す)になるときは、量子化誤差が基本波の整数倍の頻度で周期発生することになる。

[0007]

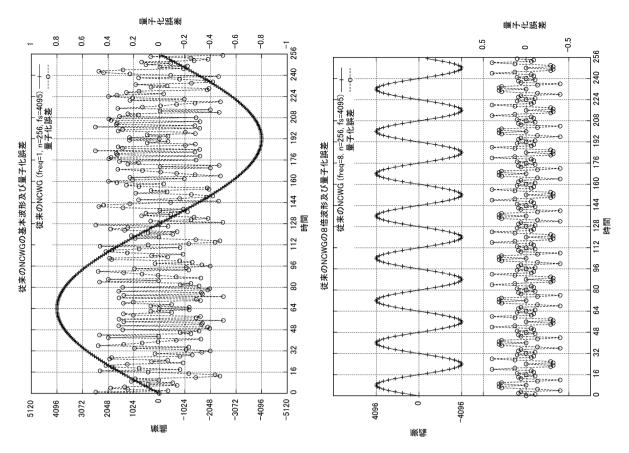

量子化誤差の説明のための簡素な例について、図1乃至図3に示す。

図1は、NCWGの基本波と、その拡大した量子化誤差を示すタイミングチャートである。

#### [00008]

図 2 は、図 1 に示した波形分割数 N = 2 5 6、フルスケール F S = ± 4 0 9 5 である 1 3 ビット x 2 5 6 ワードの正弦基本波の数表を持つ従来の N C W G の、生成する波形の基本波に対する倍数で表した周波数(以下、「freq」と略す)が freq = 8 での量子化誤差を示すタイミングチャートである。

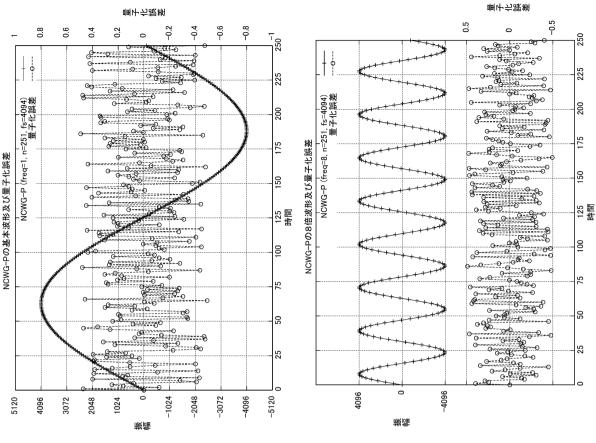

図3は、当該量子化誤差に起因するスプリアスの実例を示すタイミングチャートである

10

### [0009]

図 2 及び図 3 の従来のN C W G はいずれも、 f r e q = 8 で N の 2 5 6 に対して 1 : 3 2 の「小さな整数比」になっている場合の例である。

図 2 では「小さな整数比」になっているため、量子化誤差に顕著な周期性が発生しているのが見て取れ、この状態では、特定の周波数で大きなスプリアスを発生する事となる。

#### [0010]

図3の従来のNCWGでは量子化誤差の顕著な周期性による、特定の周波数における大きなスプリアスが見て取れる。

この状態でのスプリアスの最大値は - 8 5 . 5 1 6 d B で、そうでない場合であるN C W G - P の - 9 2 . 0 5 5 d B に比べ 6 . 5 3 9 d B 大きく、 4 d B 以上、言い換えれば電力比で倍以上悪くなっている。

20

#### [0011]

デジタル同期検波器において、NLOの波形が、図3に示すような特定の周波数において大きなスプリアスが発生する図2のような波形となった場合、その特定の周波数に雑音や妨害波があった場合には数値ミキサーの後の検波波形に妨害となって現れ、これは正規の受信信号と区別することができないため、この妨害を検波後に除去することは出来ない

0

このような状況では、検波器の性能が大きく劣化することとなる。

### [0012]

図 3 の従来のN C W G の場合では、スプリアスの最大値が、 1 3 ビットの数表のダイナミックレンジによる基準値 - 2 0 1 0 g ( 2 ^ 1 3 - 1 ) - 7 8 . 3 d B に対して - 8 5 . 5 d B であり、基準値の - 7 . 2 d B に留まってしまっているのが分かる。

30

図 2 に例を示したような、特に、半導体メモリーの容量や読み出しのためのカウンターの都合上頻繁に用いられる、 2 のべき乗を波形分割数とした N C W G では、この周期的誤差によるスプリアスの発生が顕著であり、性能の潜在的な弱点となっている。

#### [0013]

本発明は、このような状況に鑑みてなされたものであり、簡易な構成でスプリアスの発生を効果的に抑圧する数値制御波形発生器及びデジタル同期検波器を提供することを、目的とする。

【課題を解決するための手段】

40

# [0014]

本発明者は、発明が解決しようとする課題に述べたスプリアスが、数表のから生成する波形の量子化誤差の周期性に起因することに鑑み、数表の波形分割数が生成する波形の周期の小さな整数比とならない値にすれば、特定の周波数におけるスプリアスの発生が抑圧されることを見出し、本発明を完成するに至った。

特に数表の波形分割数を素数とした場合には、数表の基本波形自体に含まれる周期性以外には周期性を持たなくなるため、周期性に起因するスプリアスの発生が効果的に抑圧できる。

# [0015]

正弦波・余弦波のような振幅軸・時間軸に対して1/2周期、又は1/4周期の対称性

がある波形では、波形分割数を素数とした 1 / 2 周期、又は 1 / 4 周期の数表としてもよい。

#### [0016]

(1) 本発明の数値制御波形発生器は、基本波を表す各数値を含む数表を用いて所定の 波形を発生させる数値制御波形発生器において、

前記基本波の波形の1周期、当該基本波に振幅軸と時間軸とのうち少なくとも一方に対して対称性がある場合には当該基本の1/2周期、又は当該基本波に振幅軸及び時間軸の夫々に対して対称性がある場合には1/4周期を予め設定されたP個(Pは、1以上の整数値)の素数で、均等分割したときにおける、各時刻(各タイミング)での各振幅値を、前記各数値として含む数表と、所定の読み出し方を変える制御を実行することで、当該基本波の整数倍の波形を1以上発生させる読み出し制御部と、を備える。

10

20

30

#### [0017]

- (2) 本発明の数値制御波形発生器は、更に前記数表は、前記基本波の波形の元となる波形(アナログ波形)が、直流分を含まない波形の場合には、当該波形を示す関数の零交差点がサンプリング点とならないように位相を調整して得た整数を、前記各数値として含む。

- (3) 本発明のデジタル同期検波器は、上述の本発明の数値制御波形発生器を数値局部 発振器(NLO)として用いるデジタル同期検波器である。

#### 【発明の効果】

# [0018]

本発明によれば、簡易な構成でスプリアスの発生を効果的に抑圧する数値制御波形発生器及びデジタル同期検波器を提供することができる。

【図面の簡単な説明】

[0019]

- 【図1】従来のNCWGの基本波形と、量子化誤差を示す図である。

- 【図2】従来のNCWGによる8倍周波数波形と、その量子化誤差を示す図である。

- 【図3】2種類のNCWGの8倍周波数波での量子化誤差に起因するスプリアスの実例を示す図である。

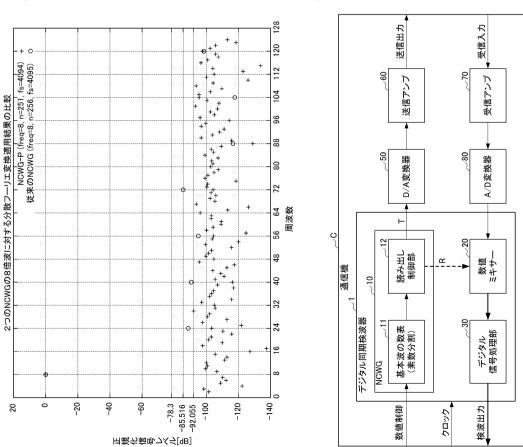

- 【図4】本発明に係るデジタル同期検波回路の構成を示すブロック図である。

- 【図5】本発明に係るNCWGの基本波形と、その量子化誤差を示す図である。

- 【図6】本発明に係るNCWGによる8倍周波数波形と、その量子化誤差を示す図である

【図7】2種類のNCWGの基本波での量子化誤差に起因するスプリアスの実例を示す図である。

【図8】2種類のNCWGの1~999倍周波数波での量子化誤差に起因するスプリアスの最大値を示す図である。

【発明を実施するための形態】

[0020]

以下、本発明の実施形態について図面を用いて説明する。

図4は、本発明が適用されるFPGA、CPLD、DSP、マイクロプロセッサ及びメモリー等のデジタル信号処理回路によって構成されるデジタル同期検波器1と、D/A変換器50、A/D変換器80、入出力アンプ60、70によって構成されるデジタル同期検波回路のブロック図である。

40

### [0021]

図4に示すデジタル同期検波器1は、NCWG10と、数値ミキサー20と、デジタル信号処理部30とを含み、D/A変換器50と、A/D変換器80とに接続されている。

ここで、NCWG10は更に、基本波の数表(素数分割)11と、読み出し制御部12とを含んでいる。

[0022]

また、D/A変換器50は、送信アンプ60と接続されており、A/D変換器80は、

受信アンプ70と接続されている。

本発明は、FPGA、CPLD、DSP、マイクロプロセッサ及びメモリー等のデジタル信号処理回路によって構成されるデジタル同期検波器又はデジタル同期周波数変換器において、発生波形の基本波の波形分割数を素数とし、正弦波・余弦波のような振幅軸・時間軸に対して1/2周期又は1/4周期の対称性がある波形では、基本波の1/2周期、又は1/4周期を素数P個に均等分割したときの各値を整数の数表として具備した数値的局部発振器及びデジタル同期検波器として実施される。

#### [0023]

図中の四角で囲まれたデジタル同期検波器 1 が、本発明の実施形態の一つであり、数表に記憶される基本波形の波形分割数が素数であることを特徴とする。

N C W G 1 0 部は、数値制御波形発生器による数値的局部発振器であり、数表に記憶される基本周波数の整数倍の数値的信号 T と、同様に基本周波数の整数倍の 1 つ又は位相や倍数の異なる複数の数値的信号 R を生成する。

#### [0024]

数表に記憶される数値は、静的に、または外部の数値制御により動的に生成し、保存される。

A / D変換器 8 0 から入力される数値的受信信号に対して、 N C W G 1 0 は数値ミキサー 2 0 とともに検波器又は周波数変換器として働く。

#### [0025]

即ち、NCWG10は、RがTと同じ信号に設定された場合には、デジタル同期検波器は単純なホモダインの同期検波器として働き、また、RがTと倍数の違う信号に設定された場合には、コヒーレント位相周波数変換器として働き、また、Rが正弦波及び余弦波のような直交する信号に設定された場合には、直交ベクトル同期検波器として働く。

また、NCWG10は、Rが複数の周波数の直交する信号に設定された時には、同時多周波の同期検波器として働く。

#### [0026]

図1は、従来のNCWGの基本波形と、量子化誤差を示す図である。

図5は、本発明に係るNCWGの基本波形と、その量子化誤差を示す図であり、即ち波形分割数を素数とした例である。

# [0027]

図 1 及び図 5 は、横軸には時間を、縦軸には量子化振幅、及び拡大して示した量子化誤差を採るグラフで、各時間における値を両者重ねてプロットしたものである。

縦軸に量子化振幅を採った点列については、いずれも正弦波形の各時間における振幅に 近い値を取っていることが分かる。

# [0028]

また縦軸に、量子化振幅の振幅との差である量子化誤差を拡大して示した採った点列については、いずれも顕著な周期性は見受けられないことが分かる。

なお、素数とは図5では具体的には251であるが、本発明に係る素数は251に限定されるものではなく、これは一例に過ぎない。

## [0029]

この波形分割数 N = 2 5 1 の正弦波の数表を持つ N C W G (以下「 N C W G - P 」と略す)を示す。

なお、波形分割数が3以上の素数、即ち奇数個に分割すると、基本波の波形の元となる 関数が直流分を含まないものであっても量子化誤差により量子化振幅が非対称となり、発 生させる波形に本来無いはずの直流分が発生する場合がある。

# [0030]

これについては、フルスケールの設定の調整により、発生させる全ての波形において無用な直流分が発生しないようにする必要がある。

その例として、前記NCWG-Pでは、波形分割数が251であるが、フルスケールを符号付き15ビット整数の最大値±4095とした場合には、発生させる信号により直流

10

20

30

40

分の発生があるため、フルスケールを直流分が生じない±4094に調整している。

#### [0031]

図 2 は、従来の N C W G による 8 倍波形を上段に示し、拡大したその量子化誤差を下段に示した図である。

図 6 は、本発明に係るNCWG-Pによる8倍波形を上段に示し、拡大したその量子化誤差を下段に示した図である。

図6におけるNCWG-Pは、図2における従来のNCWGと同じfreq=8の設定であるが、NCWG-Pでは基本波の段階で波形分割数を素数としたことから、量子化誤差には従来のNCWGの様な顕著な周期性が、見られなくなっている。

#### [0032]

図7は、2種類のNCWGの基本波での量子化誤差に起因するスプリアスの実例を示す 図である。

図3は、2種類のNCWGの8倍周波数波での量子化誤差に起因するスプリアスの実例を示す図である。

#### [0033]

図7及び図3は、横軸には周波数を、縦軸には正規化信号レベル [d B]を採るグラフで、各周波数における2つのNCWGの正規化信号レベルを重ねてプロットしたものである。

図 7 では、N C W G - P の最大スプリアス - 9 2 . 0 5 5 は、従来のN C W G の最大スプリアスを比較的小幅ではあるが下回っていることが分かる。

#### [0034]

図3では、NCWG-Pで発生するスプリアスは、8倍周波数波において、8周期毎でしか周期性を持たないことから特定の周波数にスプリアスが集中せず、従来のNCWGに比べ、6.5dB以上少なくなっている。

フルスケールを 1 6 ビットに拡張したものや、波形分割数が何万というものでも、スプリアスの発生機構は変わらないため、波形分割数 N を素数とした場合には、波形分割数が例えば 2 の冪や小さな素数の積のものに比べて、発生するスプリアスの最大値が小さくなっている。

### [0035]

本発明に伴って行った多くのシミュレーション結果により、波形分割数が例えば2の冪や小さな素数の積のものに比べ、波形分割数を素数とすることにより、発生するスプリアスの最大値がおよそ6dB低減するという知見が得られている。

逆に波形分割数が、小さな数の積になっている場合では発生するスプリアスの最大値が 酷く大きくなる場合がある。

#### [0036]

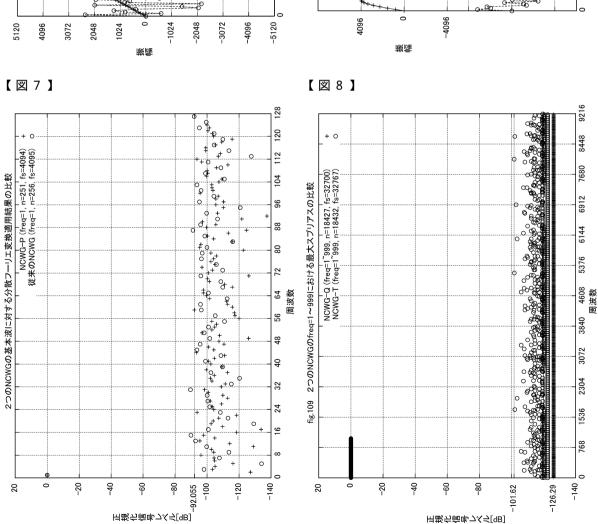

次に図8を用いて、本発明の実効性を説明する。

図 8 はフルスケールが 1 6 ビットの 2 種類の N C W G で基本波の周波数の倍数 f r e q が 1 ~ 9 9 9 の正弦波を生成した時に発生する各 f r e q で発生するスプリアスの最大値をプロットしたものである。

図 8 中、波形分割数が 1 8 4 3 2 = 2 ^ 1 1  $\times$  3 ^ 2 の N C W G - T では、 1 6 ビットの数表のダイナミックレンジによる基準値 - 2 0 1 o g (2 ^ 1 6 - 1)約 - 9 6 . 3 d B に対してスプリアスの最大値が - 9 4 . 1 d B であり、基準値よりも大きい + 2 . 2 d B あるのがわかる。

# [0037]

一方、波形分割数を同程度の大きさの素数 1 8 4 2 7 にした N C W G - Q の例では、 - 1 2 0 . 7 4 d B であり - 2 0 l o g (2 ^ 1 6 - 4 1 9 ) 9 6 . 3 d B の基準値に対してスプリアスの最大値が - 2 4 . 5 d B も低くなっていて、波形分割数を素数にすることによるスプリアス低減効果が如実にあらわれている。

#### [0038]

NCWGは分割数を夫々素数とした1/2周期、1/4周期の波形数表から、その対称

10

20

30

40

性を利用して、正弦波形、余弦波形を生成することができる。

このような手法は、夫々直交ベクトル検波や差動検波に適用がある。

#### [0039]

N C W G は、 1 / 2 周期、 1 / 4 周期の波形を素数分割した数表から、その対称性を利用して 3 つの異なる周波数の正弦波を同時に生成して 1 つの合成波形を生成することが出来る。

このような手法は、多チャネル同時検波や高調波検知等に適用がある。

### [0040]

本発明では波形分割数が2の冪や小さな数の積であるような一般的NCWGの量子化ビット数を1ビット又はそれ以上増加させたのと同程度の効果が得られるため、メモリーや数値ミキサーに使われる乗算器などのハードウェアの制限の中で、同程度のハードウェア規模においてデジタル同期検波器の検知限界の性能を一段向上することができる。

また、発生させる信号によってスプリアスが大きく変動することがないため出力信号の 信頼度が向上する。

### 【符号の説明】

#### [0041]

C・・・通信機

1・・・デジタル同期検波器

1 0 · · · N C W G

11・・・基本波の数表(素数分割)

12・・・読み出し制御部

20・・・数値ミキサー

30・・・デジタル信号処理部

50・・・D/A 変換器

60・・・送信アンプ

70・・・受信アンプ

80 · · · A / D 変換器

### 【要約】

【課題】簡易な構成でスプリアスの発生を効果的に抑圧する数値制御波形発生器及びデジタル同期検波器を提供すること。

【解決手段】本発明の数値制御波形発生器1は、基本波を表す各数値を含む数表11を用いて所定の波形を発生させる数値制御波形発生器1において、前記基本波の波形の1周期、当該基本波に振幅軸と時間軸とのうち少なくとも一方に対して対称性がある場合には当該基本の1/2周期、又は当該基本波に振幅軸及び時間軸の夫々に対して対称性がある場合には1/4周期を予め設定されたP個(Pは、1以上の整数値)の素数で、均等分割したときにおける、各時刻(各タイミング)での各振幅値を、前記各数値として含む数表11と、所定の読み出し方を変える制御を実行することで、当該基本波の整数倍周波数の波形を1以上発生させる読み出し制御部12と、を備える。

## 【選択図】図4

10

20

【図1】 【図2】

【図5】 【図6】

# フロントページの続き

(56)参考文献 特開2012-060600(JP,A)

特開昭53-081050(JP,A)

特開平08-032350(JP,A)

特開2002-271143(JP,A)

特開2013-219726(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 3 B 2 8 / 0 0

IEEE Xplore